# A Path Finding Based SI Design Methodology for 3D Integration Post Paper using 3DPF V3.0

# **Post Paper Test Cases using V3.0**

**Enable analysis with TSV/Planar metal and modeling TSV** versus microvia

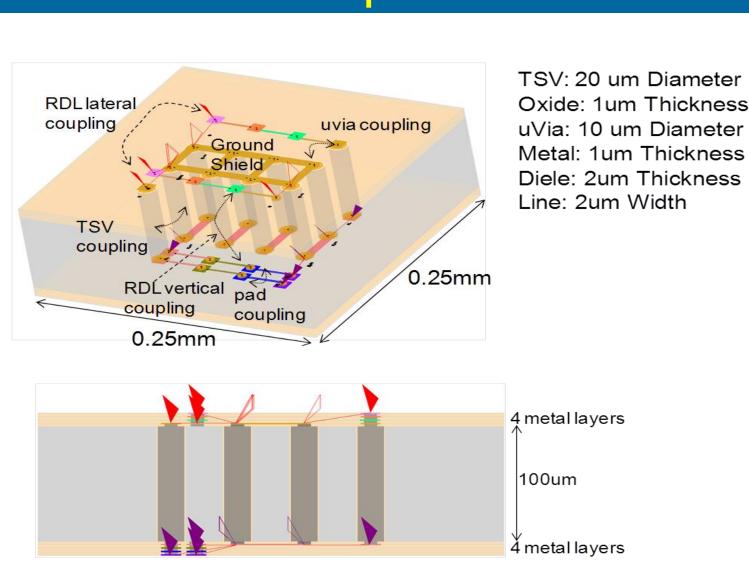

### Example 4: small 0.25mm<sup>2</sup> area silicon interposer

Analyze considerable coupling in spite of ground shield. Ground shield is in the form of grounded TSVs

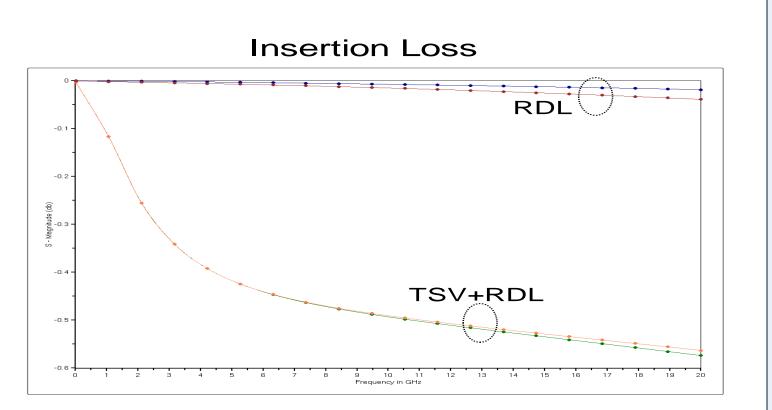

# Responses: small 0.25mm<sup>2</sup> area silicon interposer

RDL for this structure has minimal IL degradation since they are routed above or below silicon substrate, while TSV/RDL paths have ~14X worse IL

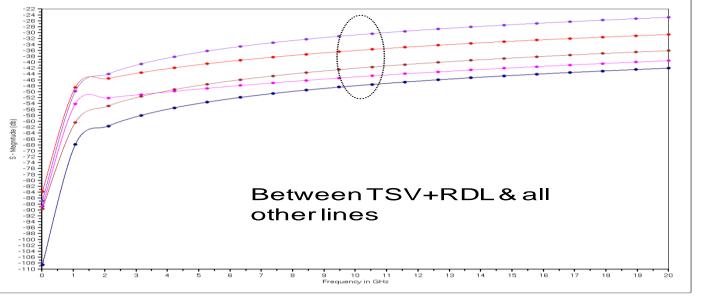

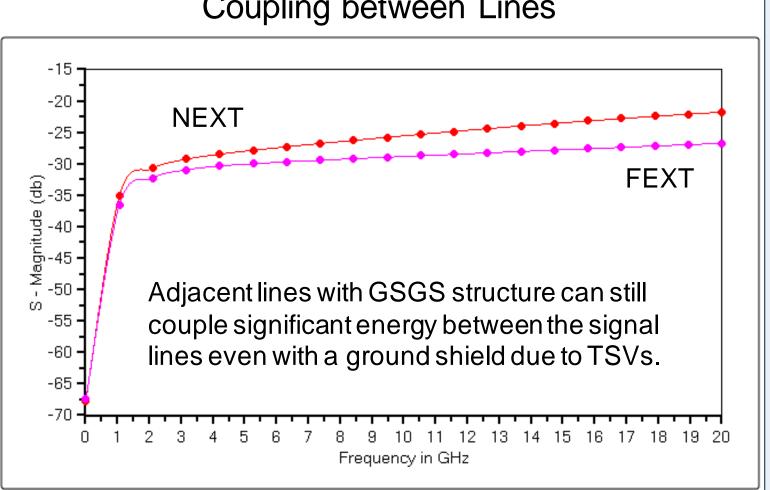

# Coupling

In spite of the ground shield using multiple TSVs, the coupling can still be high. In this example the coupling is between -24 to -48 dB.

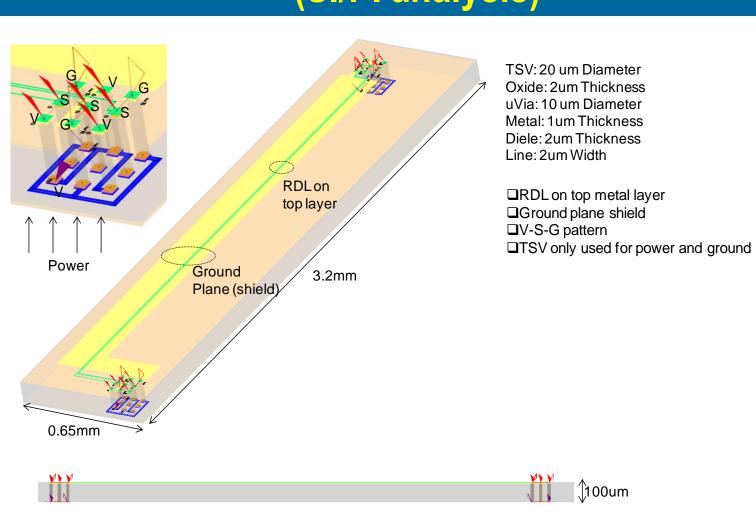

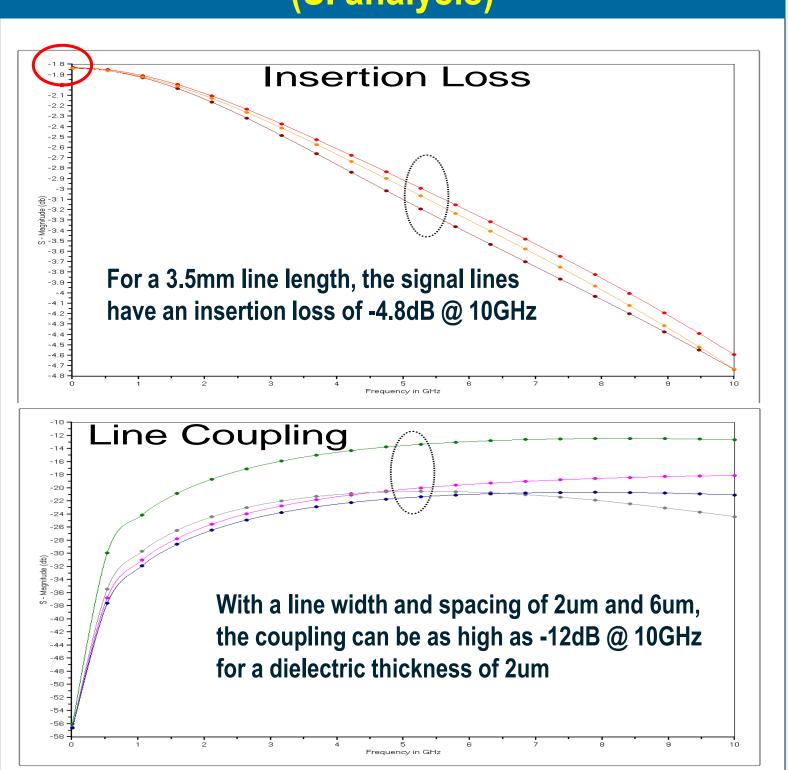

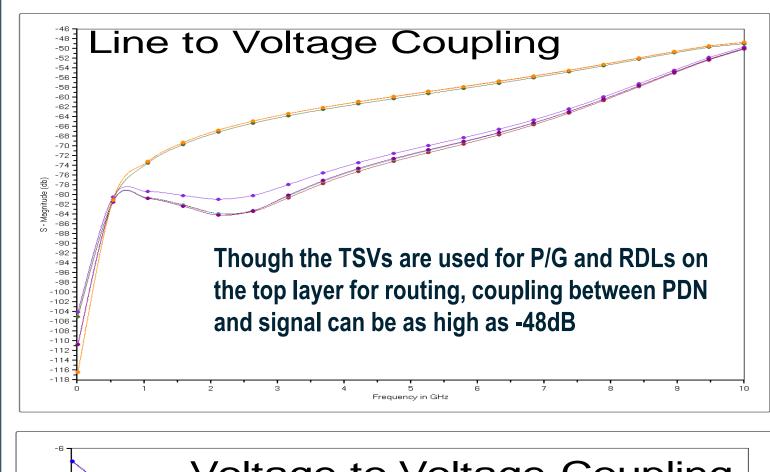

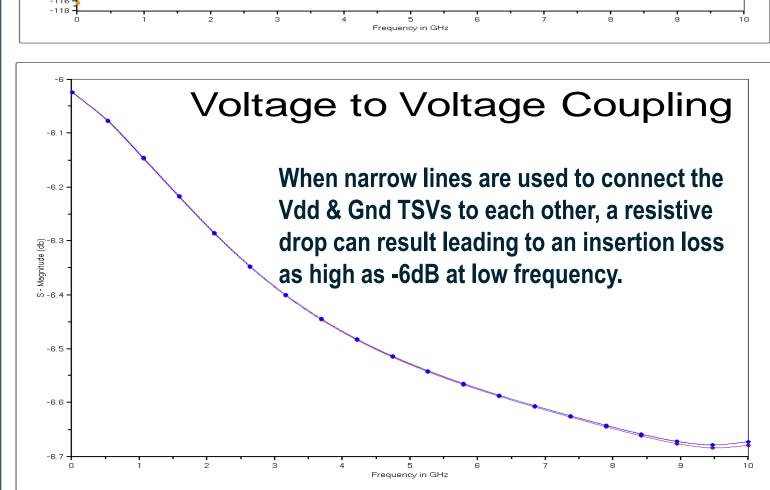

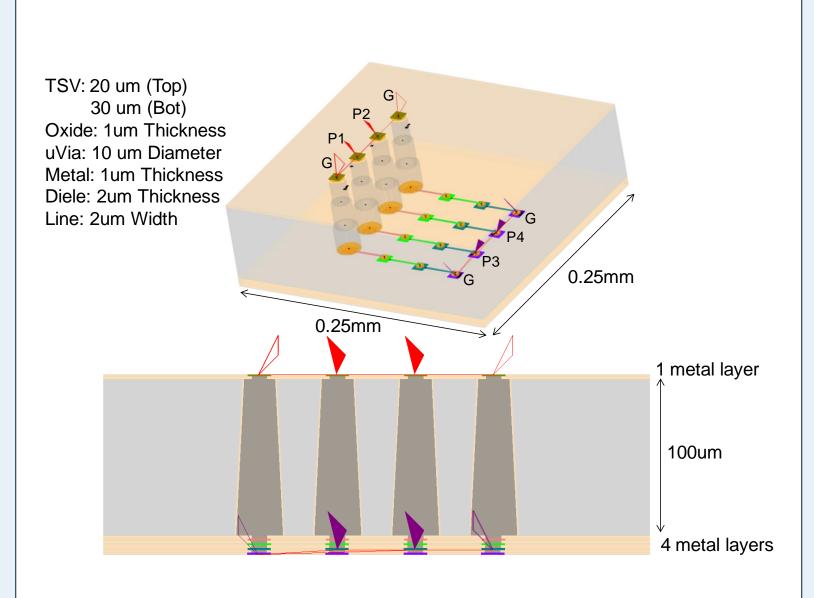

# **Example 5: Chip-to-Chip with Interposer** (SI/PI analysis)

Analyze the coupling between signal and power distribution

# Responses: Chip-to-Chip with Interposer (SI analysis)

# **Responses: Chip-to-Chip with Interposer** (PI analysis)

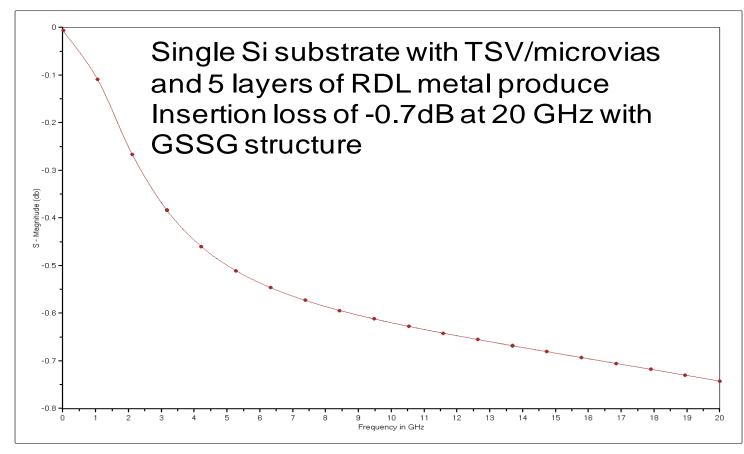

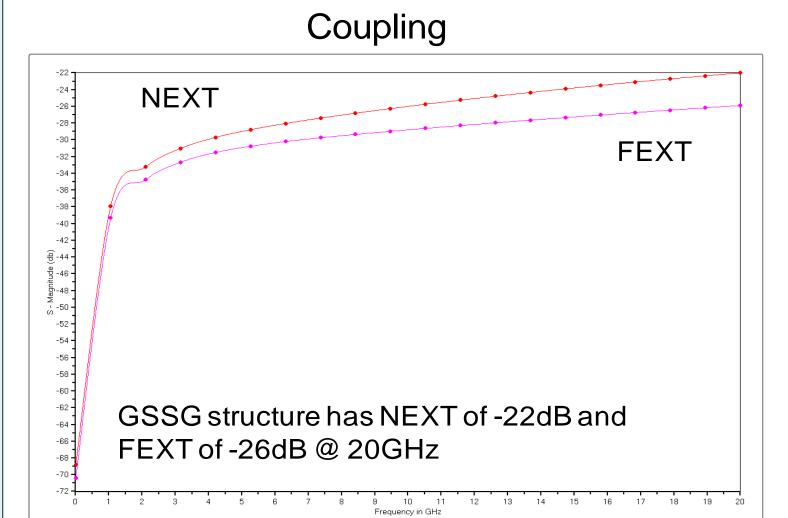

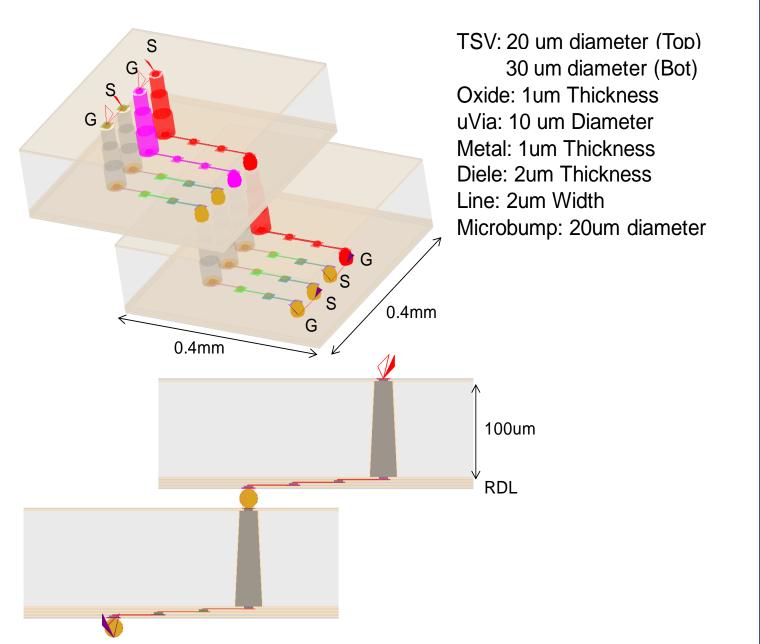

# **Example 6: Tapered TSV with RDL**

Analyze effect of tapered TSV, RDL, microvias and pads on insertion loss and coupling for a single IC

# **Responses: Tapered TSV with RDL**

# **Insertion Loss**

Intentionally left blank

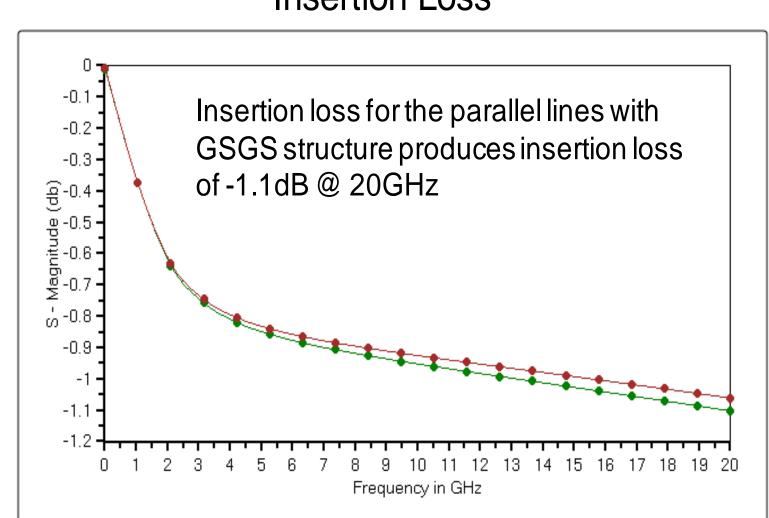

# **Example 7: Two Chip Stack**

Analyze impact of stacking 2 IC blocks with TSV and solder bumps: Insertion loss and Xtalk

#### **Responses: Two Chip Stack**

#### **Insertion Loss**

### Coupling between Lines

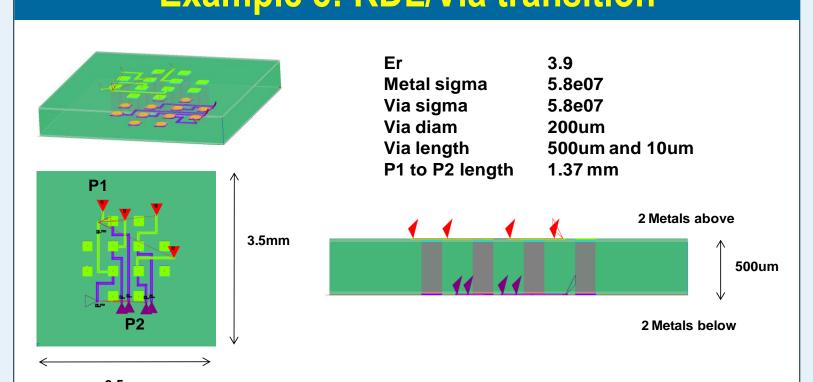

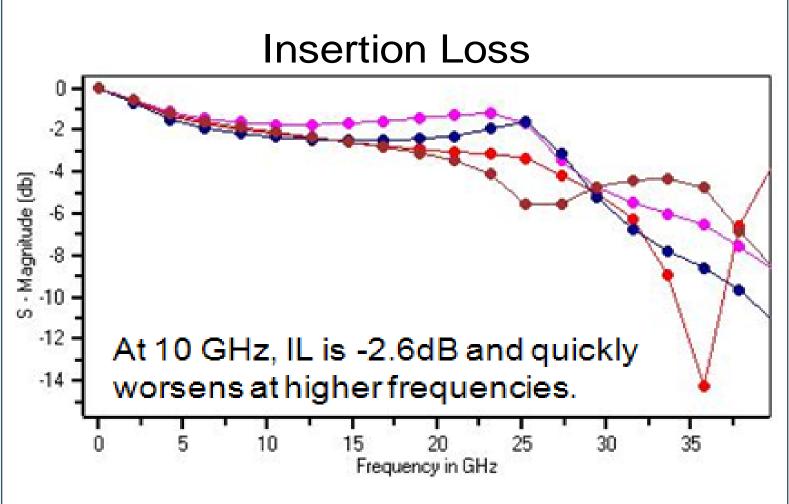

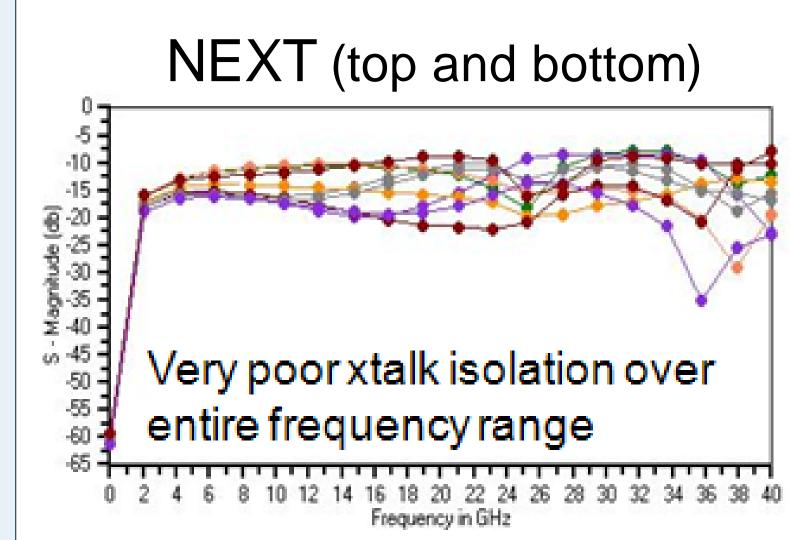

# **Example 8: RDL/Via transition**

Analyze: IL and Xtalk for short RDL and via transitions

# **Responses: RDL/Via transition**

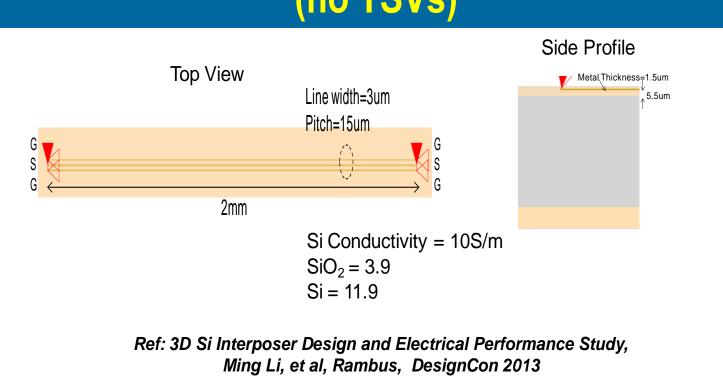

## **Example 9: Unshielded lines in Si Interposer** (no TSVs)

**Analyze: Insertion and Return Losses for GSG structure**

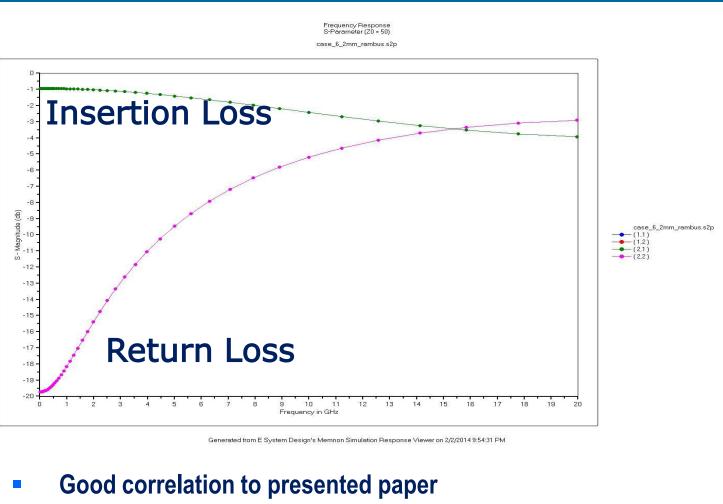

# Responses: Unshielded lines in Si Interposer (no TSVs)

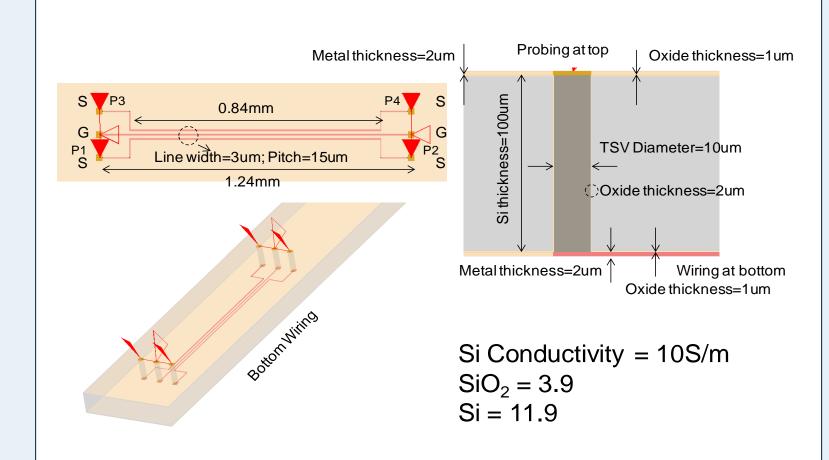

#### Example 10: Unshielded lines in Si Interposer

**Analyze: Impact of Si Conductivity on Insertion Loss?**

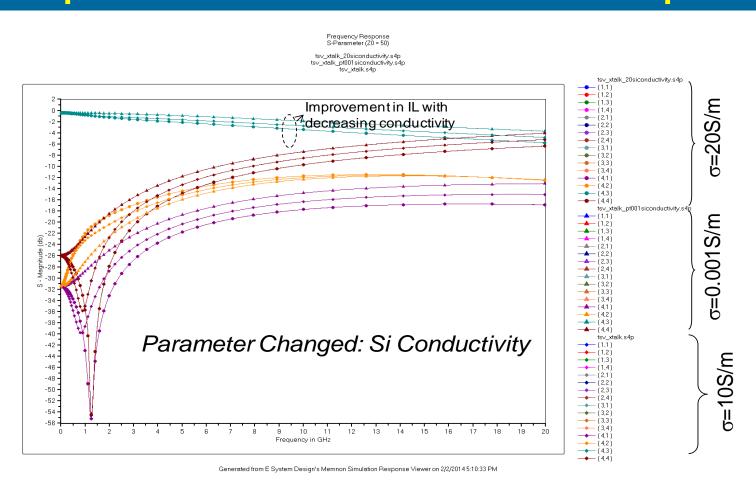

# Responses: Unshielded lines in Si Interposer

Improved Insertion Loss with decreasing conductivity

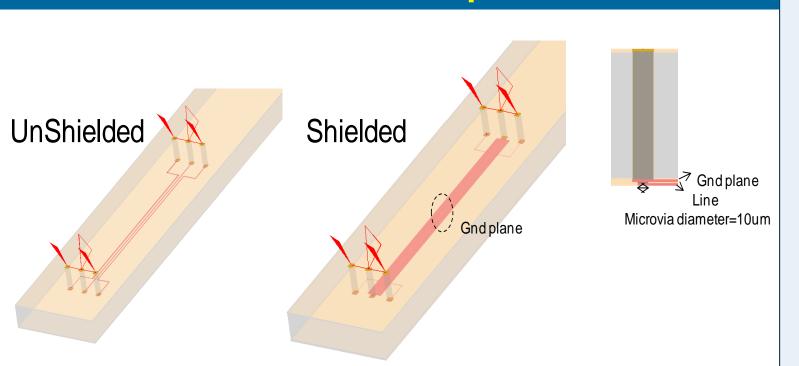

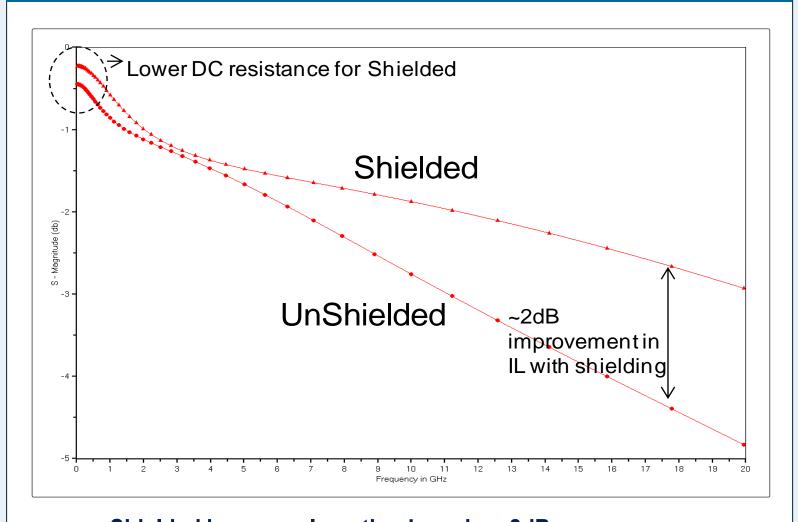

## **Example 11: Unshielded versus Shielded** lines in Si Interposer

Compare performance of shielded and unshielded lines (SGS) in Si Interposer

# Responses: Unshielded versus Shielded lines in Si Interposer

Shielded improves Insertion Loss by ~2dB Lower DC resistance for Shielded

www.PosterPresentations.c